【導讀】鎖相環(huán)(PLL)電路是由壓控振蕩器(VCO)和鑒相器組成的反饋系統(tǒng),振蕩器信號跟蹤施加的頻率或相位調制信號是否具有正確的頻率和相位。需要從固定低頻率信號生成穩(wěn)定的高輸出頻率時,或者需要頻率快速變化時,都可以使用PLL。典型應用包括采用高頻率、電信和測量技術實現(xiàn)濾波、調制和解調,以及實現(xiàn)頻率合成。

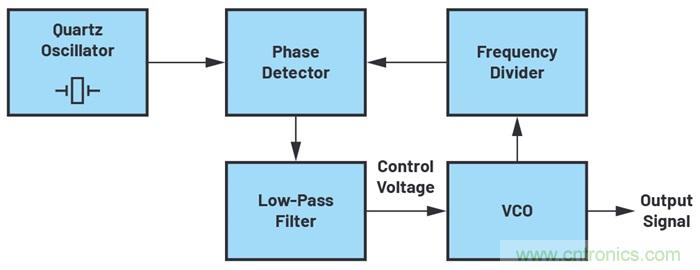

圖1所示為基于PLL的頻率合成器框圖。VCO生成輸出信號。通過PLL將其保持在設定頻率,并鎖定到基準頻率?;鶞暑l率通常由非常精準的石英振蕩器提供。在鎖相環(huán)電路的反饋路徑部分,在鑒相器前通過分頻器提供可調的VCO分頻比。

圖1. 鎖相環(huán)框圖。

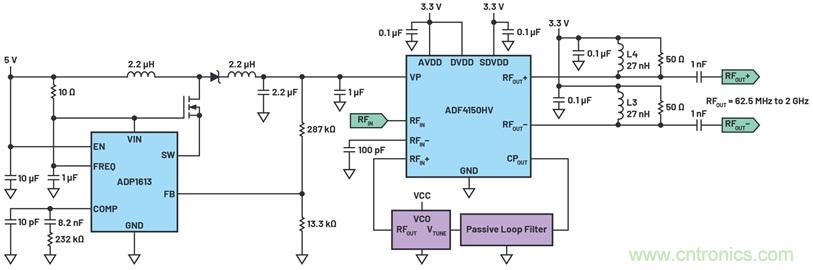

VCO包含可調的調諧元件,例如電容隨輸入電壓改變的變容二極管。因此,PLL電路可以算一種VCO反饋控制系統(tǒng)。VCO所需的輸入或控制電壓通常高于提給PLL電路的電源電壓。電源電壓一般為3.3 V或5 V,而VCO根據(jù)頻率需求可能需要高于20 V的電壓。要生成范圍更廣泛的頻率,可以使用具備更廣泛調諧范圍的VCO。圖2顯示了支持千兆赫范圍VCO的簡單電路示例。

圖2. 用于ADF4150HV的高壓電荷泵電源簡化電路。

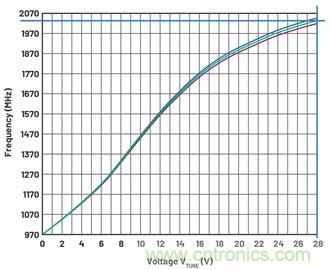

AVCO可以使用Synergy Microwave Corporation的DCYS100200-12。該產品在 28 V (VTUNE)時產生2 GHz頻率,如圖3所示。

圖3. DCYS100200-12的控制電壓與頻率關系曲線。1

生成高控制電壓,有幾種可行方案。其一是使用有源環(huán)路濾波器,該濾波器基本是由高速放大器和低通濾波器構成,可以將來自鑒相器(CPOUT)的輸出脈沖轉化為干凈的直流電壓?;蛘撸梢允褂脦Ъ呻姾杀玫腜LL頻率合成器,例如ADI的 ADF4150HV該器件不需要額外的有源環(huán)路濾波器。雖然這兩種解決方案都需要高壓電源,但是使用ADF4150HV可以減少所需的組件數(shù)量。 也可以避免有源濾波放大器導致的失真和相位噪聲。此外,ADF4150HV允許實現(xiàn)小數(shù)N或整數(shù)N鎖相環(huán)頻率合成器。最終VCO的頻率可以進行1、2、4、8或16分頻,使得輸出頻率最低可達到31.25 MHz。

ADF4150HV的集成電荷泵所需的高電壓可以使用直流-直流升壓轉 換器ADP1613生成,且不降低PLL性能。 ADP1613是一款集成功率晶體管的高效開關穩(wěn)壓器,可以輕松實現(xiàn)最高20V的輸出電壓。也可以使用額外的外部組件實現(xiàn)更高的輸出電壓,尤其是通過外部功率晶體管實現(xiàn)。ADP1613的開關頻率可在650 kHz至1.3 MHz范圍內調節(jié)。這樣可以實現(xiàn)更出色的瞬態(tài)響應和簡單的噪聲過濾。 一般而言,推薦選擇高于1 MHz的開關頻率,以便通過PLL環(huán)路濾波器降低開關噪聲。

采用ADF4150HV的鎖相環(huán)頻率合成器電路通過使用集成的RF分頻器,提供超寬帶PLL功能。工作頻率范圍為62.5 MHz至2 Ghz。通過采用相同的PLL硬件設計,可以為系統(tǒng)中的多個不同的硬件平臺 生成不同的頻率。但是,如果要求一項設計適用于不同的VCO類型,則需要在設計中集成相應的環(huán)路濾波器。這樣才能確保鎖相環(huán)可靠運行。為了實現(xiàn)相對較寬的輸出頻率調節(jié)范圍,以及相關的更高輸出功率,ADF4150HV的每個RF輸出也需要采用小型濾波器。將27 nH電感和50 Ω電阻并聯(lián),可以有效調節(jié)高達3 GHz的頻率。該電阻提供定義上的輸出阻抗較低的電感將導致頻段擴展到較低的范圍。

如今,也可提供適用于更大頻率范圍(即適用于PLL、濾波器和VCO)的一體化集成解決方案,但是,由于不同組件之間的距離過近,可能導致無用耦合。分立式設計和由此實現(xiàn)的物理分隔可以充分降低這種風險。

PLL頻率合成器模擬工具ADIsimPLL™ 也可以為HF功能模塊開發(fā)和HF信號鏈器件建模提供有效幫助。通過使用該工具,設計人員更容易模擬所有會影響PLL性能的重要非線性效應;例如,頻率合成過程中出現(xiàn)的無用雜散(雜散頻率)。

參考電路

1 "壓控振蕩器表面貼裝型號:DCYS100200-12。" Synergy Microwave Corporation,2014年10月。

"電路筆記CN-0228:單電源為28 V、高壓鎖相環(huán)(PLL)頻率合成器 供電。" ADI公司,2014年6月。

推薦閱讀: